# N-Channel Enhancement Mode Field Effect Transistor

- Features

- N-channel, normal leve

- Very low on-resistance R<sub>DS(on)</sub>

- 150 °C operating temperature

- Pb-free lead plating; RoHS compliant

- Qualified according to JEDEC for target application

- Ideal for high-frequency switching and synchronous rectification

#### Pin Configurations(TO252)

**Top View**

# N-Channel MOSFET

## Absolute Maximum Ratings TA=25°C unless otherwise noted

| Parameter                                        |            | Symbol                            | Ratings                                 | Unit |

|--------------------------------------------------|------------|-----------------------------------|-----------------------------------------|------|

| Drain-Source Voltage                             |            | V <sub>DSS</sub>                  | 60                                      | V    |

| Gate-Source Voltage                              |            | V <sub>GSS</sub>                  | ±20                                     | V    |

| Drain Current                                    | Continuous | I <sub>D</sub>                    | 5 <sup>(1A)</sup><br>20 <sup>(1B)</sup> | A    |

|                                                  | Pulse      | I <sub>DM</sub>                   | 60                                      |      |

| Total Power Dissipation (note1)                  |            | P <sub>D</sub>                    | 0.8 <sup>(1A)</sup>                     | W    |

|                                                  |            | D                                 | 25 <sup>(1B)</sup>                      |      |

| Operating and Storage Junction Temperature Range |            | T <sub>J</sub> , T <sub>STG</sub> | -55 to +150                             | °C   |

Notes

- 1A、Surface Mounted on 1x1FR4 Board.

- 2. The value of PD is measured with the device mounted on 1in 2 FR-4 board with 2oz. Copper, in a still air environment with TA =25° C. The value in any given application depends on the user's specific board design. The current rating is based on the DC thermal resistance rating and PCB layout: A. Minimum footprint; B. With additional heat sink.

- 3. Repetitive rating, pulse width limited by junction temperature

### Product Summary

| V <sub>DS</sub> | $V_{\text{GS}}$ | Test Conditions | R <sub>DS(on)</sub> |

|-----------------|-----------------|-----------------|---------------------|

| 60V             | . 201/          | 5A@VGS=10V      | 35mR                |

| 60V ±20V        | 4.5A@ VGS=4V5   | 40mR            |                     |

FS2246

# • Electrical Characteristics (T<sub>A</sub>=25°C unless otherwise noted)

| Parameter <sup>(note2)</sup>      | Symbol               | Test Conditions                                                         | Min | Тур  | Max  | Unit |

|-----------------------------------|----------------------|-------------------------------------------------------------------------|-----|------|------|------|

| Drain-Source Breakdown Voltage    | V <sub>(BR)DSS</sub> | V <sub>GS</sub> = 0 V, I <sub>D</sub> = 250 uA                          | 60  |      |      | V    |

| Zero Gate Voltage Drain Current   | I <sub>DSS</sub>     | $V_{DS}^{}=60 \text{ V}, \text{ V}_{GS}^{}=0 \text{ V}$                 |     | -    | 1    | uA   |

| Gate–Body Leakage                 | l<br><sub>GSS</sub>  | $V_{_{\rm GS}} = \pm 20 \text{ V}, \text{ V}_{_{\rm DS}} = 0 \text{ V}$ |     | -    | ±100 | nA   |

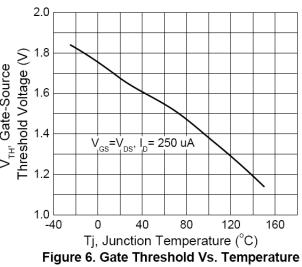

| Gate Threshold Voltage            | V <sub>GS(TH)</sub>  | $V_{DS} = V_{GS}, I_{D} = 250 \text{ uA}$                               | 1   | 1.4  | 3    | V    |

| Static Drain–Source On–Resistance | R <sub>DS(ON)</sub>  | $V_{gs}$ = 10 V, I <sub>D</sub> = 5.0 A                                 |     | 35   | 41   | mR   |

|                                   |                      | V <sub>GS</sub> = 4.5 V, I <sub>D</sub> = 4.5 A                         |     | 40   | 55   |      |

| Input Capacitance                 | C <sub>ISS</sub>     | V <sub>DS</sub> = 10 V, V <sub>GS</sub> = 0 V,                          |     | 1180 |      | pF   |

|                                   |                      | F = 1MHz                                                                |     |      |      |      |

| Output Capacitance                | C <sub>oss</sub>     |                                                                         |     | 170  |      |      |

| Reverse Transfer Capacitance      | C <sub>RSS</sub>     |                                                                         |     | 100  |      |      |

| Turn–On Delay Time                | T <sub>D(ON)</sub>   | V <sub>GS</sub> =10V, V <sub>DS</sub> =30V,                             |     |      | 25   | nS   |

|                                   |                      | R <sub>L</sub> =5.4R,                                                   |     |      |      |      |

|                                   |                      | R <sub>GEN</sub> =3R, I <sub>D</sub> =5.5A                              |     |      |      |      |

| Turn–On Rise Time                 | T <sub>R</sub>       |                                                                         |     |      | 70   |      |

| Turn–Off Delay Tim                | T <sub>D(OFF)</sub>  | 1                                                                       |     |      | 300  |      |

| Turn–Off Fall Time                | T <sub>F</sub>       | 1                                                                       |     |      | 150  |      |

| Diode Forward Voltage             | V <sub>SD</sub>      | V <sub>GS</sub> = 0 V, I <sub>S</sub> = 2 A                             | 0.5 | 0.77 | 1.0  | V    |

The value of PD is measured with the device mounted on 1 in 2 FR-4 board with 2oz. Copper, in a still air environment with TA =25° C. The value in any given application depends on the user's specific board design. The current rating is based on the DC thermal resistance rating and PCB layout: A. Minimum footprint; B. With additional heat sink.

2. Repetitive rating, pulse width limited by junction temperature

V<sub>DS</sub>= 5V

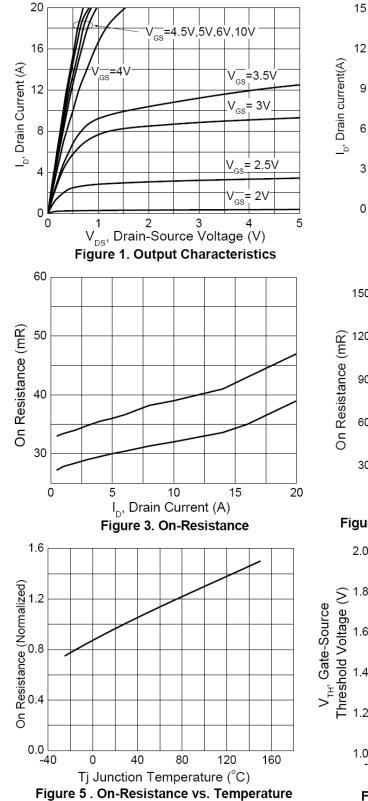

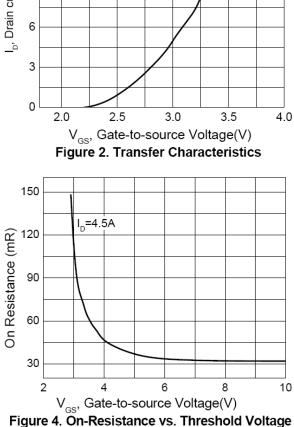

# • TYPICAL CHARACTERISTICS (25°C UNLESS NOTED)

### • Package Information

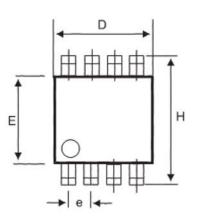

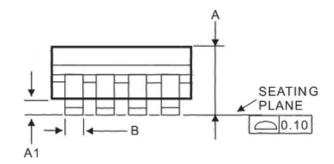

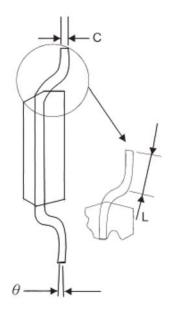

# SOP-8 Package Outline

| DIM | MILLIMETERS (mm) |            |  |

|-----|------------------|------------|--|

| DIM | MIN              | MAX        |  |

| А   | 1.35             | 1.75       |  |

| A1  | 0.10             | 0.25       |  |

| В   | 0.35             | 0.49       |  |

| с   | 0.18             | 0.25       |  |

| D   | 4.80             | 5.00       |  |

| E   | 3.80             | 4.00       |  |

| е   | 1.27 BSC         |            |  |

| н   | 5.80             | 6.20       |  |

| L   | 0.40             | 1.25       |  |

| θ   | 0°               | <b>7</b> ° |  |

#### Note: 1. Refer to JEDEC MS-012AA.

2. Dimension "D" does not include mold flash, protrusions or gate burrs . Mold flash, protrusions or gate burrs shall not exceed 0.15 mm per side.